#### **Features**

- Maximum Sample Rate

- o Max. 32 GHz

- 2/4/8/16/32 GHz options

- Number of Channels: total 34 CH

- Single-ended channels (31 CH)

- Per-pin termination level

- Per-pin threshold level

- Per-pin timing delay

- Differential channels (3 CH)

- 1 Differential clock input (CK)

- 2 Differential strobe input(WCK/RDQS)

- Analysis mode

- Timing mode

- Eye mode

- Acquisition Memory

- Max. 512 GB (standard 128 GB)

- Full memory depth up to 32 GHz

- Hardware data compression

- Hysteresis settings for all channels

- Host Interface: PCIe Gen3 x8

- Target application

- DDR4/5 protocol analysis

- LPDDR4/5 protocol analysis

## JKI JLA420A

## **DDR5/LPDDR5 Protocol Analyzer**

#### **Overview**

The JKI JLA420A protocol analyzer system is the industry's highest performance DDR5/LPDDR5 protocol analyzer with deep acquisition memory depth up to 512GB and highest sampling rate up to 32GHz. Our high-speed and powerful memory trace solutions enable you to debug and validate DDR based memory systems up to 6.4 Gb/s

#### **Large Memory for Data Capturing**

Large memory depth up to 512GB allows you to debug very complex problems by long capturing time.

#### **Ultra-fast Sampling Speed**

Ultra-fast sampling speed up to 32 GHz allows you to capture data rate up to 6.4 Gb/s for all channels without any extra options.

#### **Probe Solution**

To minimize signal degradation in the probe system, the analog module is separated from the digital module and placed as close as possible to the device.

## **Interposer Solution**

We provide variety of interposer and connecting solutions: LPDDR4/5 interposers, DDR4/5 DIMM interposers

### **Software Features**

- Capturing, Navigating, and Analyzing DDR memory protocol through fast TeraView 2.0 GUI.

- Easy setup and configuration window.

- Software based timing mode eye diagram.

- Programmable packet decoder and APIs for user post-analysis tool development.

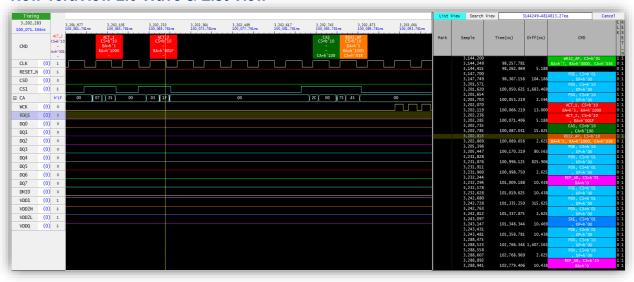

## **New TeraView 2.0 Wave & List View**

## **Timing Mode Eye Diagram**

| Channel Specification                |                                       |

|--------------------------------------|---------------------------------------|

| Number of Channels                   | 34 (31 single-ended + 3 differential) |

| Input Voltage Range                  | -0.2V to 1.2V (analyzer input)        |

| Minimum Input Voltage Swing          | 40 mV (analyzer input)                |

| Termination (Vtt) Voltage Range      | 0V to 1.2V (analyzer input)           |

| Termination (Vtt) Voltage Resolution | 1 mV                                  |

| Threshold (Vref) Voltage Range       | 0V to 1.2V (analyzer input)           |

| Threshold (Vref) Voltage Resolution  | 1 mV                                  |

| Hysteresis (Vhys) Voltage Range      | 0 ~ 50 mV                             |

| Timing Delay Range                   | -2ns to 2ns                           |

| Timing Delay Resolution              | 31.25 ps @32 GHz                      |

| Input Impedance                      | 50 Ohm (analyzer input)               |

|                                      | 250 Ohm (5:1 probe)                   |

|                                      | 500 Ohm (10:1 probe)                  |

| Acquisition Specification |                                    |

|---------------------------|------------------------------------|

| Sample Rate               | 2.0 / 4.0 / 8 / 16 / 32 GHz        |

| Analysis Mode             | Timing mode, Filter mode, Eye mode |

| Acquisition Memory        | Max. 512 GB (standard 128 GB)      |

| Host Interface            | PCIe Gen3 x8                       |

| Data Compression          | Hardware compression               |

| Data De-compression       | Software de-compression            |

| Trigger Specification |                                                  |

|-----------------------|--------------------------------------------------|

| Trigger Pattern       | E(Either edge), R(Rising edge), F(Falling edge), |

|                       | H(High), L(Low), X(Don't care) for all channel   |

| Trigger Sequence      | 2 ~ 4 burst trigger                              |

| Trigger Action        | Start capture                                    |

| Trigger Rate          | TBD                                              |

| Pre-trigger Size      | TBD                                              |

| Environmental and physical  |                            |

|-----------------------------|----------------------------|

| Power Consumption           | Max. 150W                  |

| Operation Temperature (nom) | 0 to +40 dec C             |

| Humidity (nom)              | 0 to 80% relative humidity |

| Dimensions (W x H x D)      | 347 mm x 290 mm x 74 mm    |

| Weight                      | 4.7kg                      |

# **Recommended System Configuration for DDR5**

| Model      | Qty | Description                                             |

|------------|-----|---------------------------------------------------------|

| JLA420A    | 1   | JLA420A DDR5/LPDDR5 Protocol Analyzer (128GB- standard) |

| P105Z0     | 1   | DDR5 DIMM interposer                                    |

| SW-DD5-BD  | 1   | Software – DDR5 bus decoder                             |

| PCIe-HIB38 | 1   | PCIe host adapter (Gen3 x8)                             |

| PCIe-0802  | 1   | PCIe cable 2m (Gen3 x8)                                 |

# **Recommended System Configuration for LPDDR5**

| Model      | Qty | Description                                             |

|------------|-----|---------------------------------------------------------|

| JLA420A    | 1   | JLA420A DDR5/LPDDR5 Protocol Analyzer (128GB- standard) |

| P1034B     | 1   | Samtec probe cable                                      |

| SW-LP5-BD  | 1   | Software – LPDDR5 bus decoder                           |

| PCIe-HIB38 | 1   | PCIe host adapter (Gen3 x8)                             |

| PCIe-0802  | 1   | PCIe cable 2m (Gen3 x8)                                 |

# **Ordering Information**

| Model         | Description                                                    |

|---------------|----------------------------------------------------------------|

| JLA420A       | JLA420A DDR5/LPDDR5 Protocol Analyzer (128GB- standard)        |

| - Option 256G | 256 GB memory option                                           |

| - Option 512G | 512 GB memory option                                           |

| P1034B        | Samtec probe cable                                             |

| P2134A-08S    | Connector-less probe cable                                     |

| P104Z0        | DDR4 DIMM interposer                                           |

| P105Z0        | DDR5 DIMM interposer                                           |

| PCIe-HIB38    | PCIe host adapter (Gen3 x8)                                    |

| PCIe-0802     | PCIe cable 2m (Gen3 x8)                                        |

| SW-LP5-BD     | Software – LPDDR5 bus decoder                                  |

| SW-DD5-BD     | Software – DDR5 bus decoder                                    |

| CAL-1032A     | Calibration Kits                                               |

| W200R-01      | 1-year technical service program for hardware and software     |

| W200R-03      | 3-years warranty & calibration service program (return to JKI) |