#### **Features**

- Number of Channels: 32

- Maximum Sampling Speed

- SDR mode: 2.4 Gbps with 2.4 GHz Clock (Clock divide = 2)

- □ DDR mode: 2.4 Gbps with 1.2 GHz Clock (Clock divide = 1)

- Data channel

- Per-pin termination level (1 mV Resolution)

- Per-pin threshold level (1 mV resolution)

- Per-pin timing delay (5 ps resolution)

- Source synchronous sampling

- Clock channel

- □ Differential clock input

- ☐ Clock divider & inverter circuit

- Support clock frequency changing & clock suspend timing detection

- Data Acquisition

- Acquisition memory depth: up to 64

GB

- Streaming speed: max. 4.8 GB/s through PCIe Gen3 x8

- Storage capacity: up to 16 TB SSD Raid server

- Target application

- ☐ LPDDR3, LPDDR4 protocol analysis

- DDR3, DDR4 protocol analysis

## JKI JLA320A

## LPDDR3/4 Protocol Analyzer

#### **Overview**

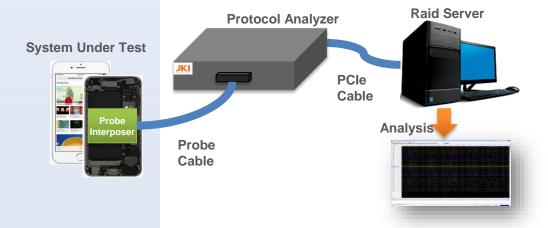

The JKI JLA320A protocol analyzer system combines reliable data capture with high bandwidth data streaming to storage server for the powerful post-analysis and validation tools to enable you to quickly and confidently validate and debug high speed digital designs operating at speeds up to 2.4 Gb/s.

## **Large Memory for Data Capturing**

Unlimited amount of storage disk space up to 16 TB allows you to debug very complex problems where the cause and symptoms may be separated by several minutes or even above 1 hour.

### **Sampling Solution**

Combining state mode for data and timing mode for clock with various clock options (divider, inverter, scan) can be used to capture mobile memory timing accurately and effectively.

#### **Probe Solution**

Use Z0 probe to capture optimum DDR4 signals with adaptive termination and equalization

## **Interposer Solution**

Our proprietary probe interposer solution allows lossless capture of LPDDR4 logic timing up to 2.4 Gb/s

## **Software Feature**

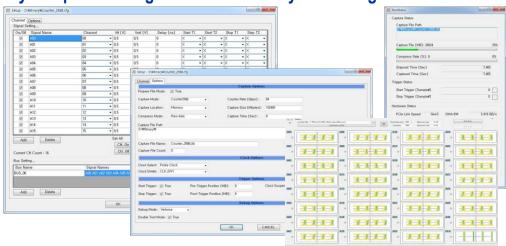

- · Easy setup and configuration tool with Eye scanning.

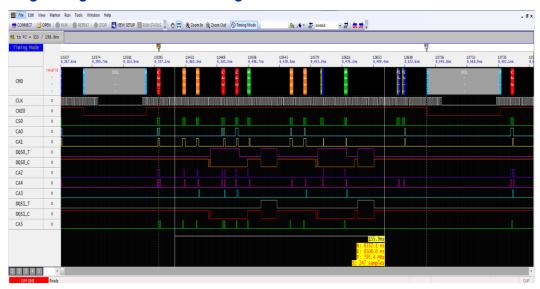

- Navigate big waveform file through our fast TeraView GUI.

- Lossless data streaming through PCle.

- Compress and decompress to reduce data size.

- Provide packet decoder API for user post-analysis tool development.

Easy setup and configuration tool with Eye scanning

## Navigate big waveform file through fast TeraView GUI

| Channel Specification          |                     |

|--------------------------------|---------------------|

| Clock channel (CLK)            | 1 differential pair |

| Data channel (DATA)            | 31 single ended     |

| Input voltage range            | -0.2 V to 1.2 V     |

| Minimum voltage swing          | 100 mV              |

| Termination voltage range      | 0 V to 1.2 V        |

| Termination voltage resolution | 1 mV                |

| Threshold voltage range        | 0 V to 1.2 V        |

| Threshold voltage resolution   | 1 mV                |

| Offset delay range             | -1.0 ns to 1.0 ns   |

| Offset delay resolution        | 5 ps                |

| Input impedance                | 50 Ohm              |

| Acquisition Specification           |                                                                              |

|-------------------------------------|------------------------------------------------------------------------------|

| Maximum data rate                   | 2.4 Gb/s                                                                     |

| Edge detection                      | single data rate (SDR) ,or double data rate (DDR)                            |

| Clock functions                     | Divider, Inverter, Clock frequency changing & clock suspend timing detection |

| On-board buffer memory size         | 16 / 32 / 64 GB                                                              |

| Streaming speed                     | PCIe Gen3 x8 (4.8 GB/s)                                                      |

| Data compression and de-compression | Hardware compression, Software de-compression                                |

| Trigger Specification |                                                     |

|-----------------------|-----------------------------------------------------|

| Maximum trigger rate  | 2.4 Gb/s                                            |

| Trigger resources     | 8 consecutive patterns: H, L, X                     |

| Trigger actions       | Start capture, Stop capture                         |

| Trigger position      | User-defined pre-trigger, User-defined post-trigger |

| Environmental and physical  |                            |

|-----------------------------|----------------------------|

| Operating temperature (nom) | 0 to +40 deg C             |

| Humidity (nom)              | 0 to 80% relative humidity |

| Dimensions (W x H x D)      | 195 mm x 60 mm x 300 mm    |

| Weight                      | 1.5 KG                     |

# JLA320A LPDDR3/4 Protocol Analyzer System Configuration - Recommended

| Model        | Qty | Description                            |

|--------------|-----|----------------------------------------|

| JLA320A      | 1   | JLA320A LPDDR3/4 Protocol Analyzer     |

| - Option 032 | 1   | 32 GB memory option                    |

| P1032B       | 1   | 32-pin single-ended probe cable type 1 |

| SW-LP4-BD    | 1   | Software – LPDDR4 bus decoder          |

| PCIe-HIB38   | 1   | PCIe host adapter (Gen3 x8)            |

| PCIe-0802    | 1   | PCIe cable 2m (Gen3 x8)                |

| RSS-8316S    | 1   | Raid storage server (16 TB SSD)        |

# **Ordering Information**

| Model        | Description                                                    |

|--------------|----------------------------------------------------------------|

| JLA320A      | JLA320A LPDDR3/4 Protocol Analyzer                             |

| - Option 032 | 32 GB memory option                                            |

| - Option 064 | 64 GB memory option                                            |

| P1032B       | 32-pin single-ended probe cable type 1                         |

| P1033B       | 32-pin single-ended probe cable type 2 (split)                 |

| P100Z0       | DDR3 DIMM interposer                                           |

| P104Z0       | DDR4 DIMM interposer                                           |

| PCIe-HIB38   | PCle host adapter (Gen3 x8)                                    |

| PCIe-0802    | PCIe cable 2m (Gen3 x8)                                        |

| SW-LP4-BD    | Software – LPDDR4 bus decoder                                  |

| SW-DD4-BD    | Software – DDR4 bus decoder                                    |

| CAL-1032A    | Calibration Kits                                               |

| RSS-8304S    | Raid storage server (4 TB SSD)                                 |

| RSS-8308S    | Raid storage server (8 TB SSD)                                 |

| RSS-8316S    | Raid storage server (16 TB SSD)                                |

| W200R-01     | 1-year technical service program for hardware and software     |

| W200R-03     | 3-years warranty & calibration service program (return to JKI) |